好文共享:理解低壓差穩(wěn)壓器,實現(xiàn)系統(tǒng)優(yōu)化設計

作者:Glenn Morita

低壓差穩(wěn)壓器(LDO)看似簡單,但可提供重要功能,例如將負載與不干凈的電源隔離開來或者構建低噪聲電源來為敏感電路供電。

本簡短教程介紹了一些常用的LDO相關術語,以及一些基本概念,如壓差、裕量電壓、靜態(tài)電流、接地電流、關斷電流、效率、直流輸入電壓和負載調(diào)整率、輸入電壓和負載瞬態(tài)響應、電源抑制比(PSRR)、輸出噪聲和精度。同時,為了方便理解,文中采用了示例和插圖。

設計過程中通常到后期才會進行LDO選型,并且很少進行分析。本文所述的概念將使設計人員能夠根據(jù)系統(tǒng)要求挑選最佳的LDO。

壓差

壓差(VDROPOUT)是指輸入電壓進一步下降而造成LDO不再能進行調(diào)節(jié)時的輸入至輸出電壓差。在壓差區(qū)域內(nèi),調(diào)整元件作用類似于電阻,阻值等于漏極至源極導通電阻(RDSON)。壓差用RDSON和負載電流表示為:

VDROPOUT = ILOAD × RDSON

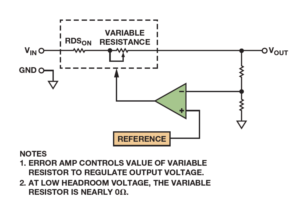

RDSON包括調(diào)整元件電阻、片內(nèi)互連電阻、引腳電阻和線焊電阻,并可通過LDO的壓差進行估算。例如,采用WLCSP封裝時,ADP151在200 mA負載下的最差情況壓差為200 mW,因此RDSON約為1.0 Ω。圖1所示為LDO的原理示意圖。在壓差模式下,可變電阻接近于零。LDO無法調(diào)節(jié)輸出電壓,因此輸入電壓和負載調(diào)整率、精度、PSRR和噪聲等其他參數(shù)都沒有意義。

圖1. LDO的原理示意圖

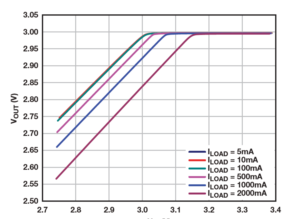

圖2顯示了3.0 V ADM7172 LDO的輸出電壓與輸入電壓之間的關系。2 A時的壓差通常為172 mW,因此RDSON約為86 mΩ。壓差區(qū)域從約3.172 V的輸入電壓下降到2.3 V。低于2.3 V時,該器件不能正常工作。負載電流越小,壓差也會按比例下降: 在1 A時,壓差為86 mV。低壓差可最大程度地提高調(diào)節(jié)器的效率。

圖2. 3.0 V ADM7172 LDO的壓差區(qū)

裕量電壓

裕量電壓是指LDO滿足其規(guī)格所需的輸入至輸出電壓差。數(shù)據(jù)手冊通常將裕量電壓作為指定其他參數(shù)時所用的條件。裕量電壓通常約為400 mV至500 mV,但有些LDO需要高達1.5 V的裕量電壓。裕量電壓不應與壓差混淆,因為只有當LDO在壓差模式下工作時這兩者才相同。

靜態(tài)電流和接地電流

靜態(tài)電流(IQ)是指當外部負載電流為零時為LDO的內(nèi)部電路供電所需的電流。它包括帶隙基準電壓源、誤差放大器、輸出分壓器以及過流和過溫檢測等電路的工作電流。靜態(tài)電流由拓撲結構、輸入電壓和溫度確定。

IQ = IIN(空載時)

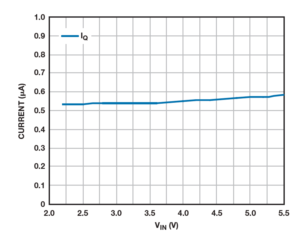

當輸入電壓在2 V和5.5 V之間變化時,ADP160 LDO的靜態(tài)電流幾乎恒定不變,如圖3所示。

圖3. ADP160 LDO的靜態(tài)電流與輸入電壓之間的關系

接地電流(IGND)是指輸入電流與輸出電流之差,并且必然包括靜態(tài)電流。低接地電流可最大程度地提高LDO效率。

IGND = IIN – IOUT

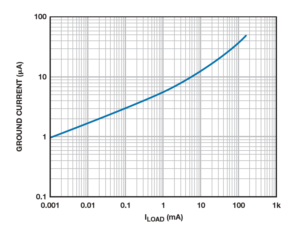

圖4顯示了ADP160 LDO的接地電流變化與負載電流之間的關系。

圖4. ADP160 LDO接地電流與負載電流之間的關系

對于高性能CMOS LDO,接地電流通常遠小于負載電流的1%。接地電流隨負載電流的增加而增加,因為PMOS調(diào)整元件的柵極驅(qū)動必須增加,以補償因其RON引起的壓降。在壓差區(qū)域內(nèi),在驅(qū)動器級開始飽和時,接地電流也會增加。對于要求具有低功耗或小偏置電流的應用而言,CMOS LDO至關重要。

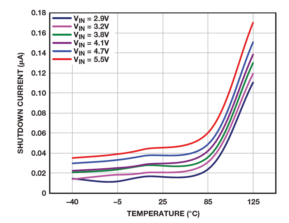

關斷電流

關斷電流是指輸出禁用時LDO消耗的輸入電流。參考電路和誤差放大器在關斷模式下都不上電。較高的漏電流會導致關斷電流隨溫度升高而增加,如圖5所示。

圖5. ADP160 LDO關斷電流與溫度之間的關系

效率

LDO的效率由接地電流和輸入/輸出電壓確定:

效率 = IOUT/(IOUT + IGND) × VOUT/VIN × 100%

若需獲得較高的效率,必須最大程度地降低裕量電壓和接地電流。此外,還必須最大程度地縮小輸入和輸出之間的電壓差。輸入至輸出電壓差是確定效率的內(nèi)在因素,與負載條件無關。例如,采用5 V電源供電時,3.3 V LDO的效率從不會超過66%,但當輸入電壓降至3.6 V時,其效率將增加到最高91.7%。LDO的功耗為(VIN – VOUT) × IOUT。

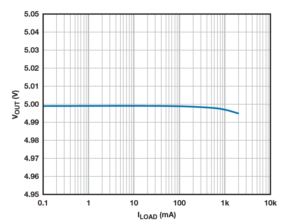

直流負載調(diào)整率

負載調(diào)整率衡量LDO在負載條件變化時仍保持額定輸出電壓的能力。負載調(diào)整率定義如下(如圖6所示):

負載調(diào)整率 = ΔVOUT/ΔIOUT

圖6. ADM7172 LDO輸出電壓和負載電流之間的關系

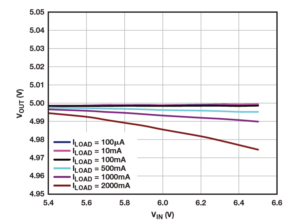

直流輸入電壓調(diào)整率 輸入電壓調(diào)整率是衡量LDO在輸入電壓變化時仍保持規(guī)定輸出電壓的能力。輸入電壓調(diào)整率定義為:

輸入電壓調(diào)整率 = ΔVOUT/ΔVIN。

圖7顯示了不同負載電流條件下ADM7172的輸出電壓與輸入電壓之間的關系圖。輸入電壓調(diào)整率隨著負載電流增加而變差,原因是LDO的總環(huán)路增益不斷降低。此外,LDO的功耗也隨輸入至輸出電壓差增加而增加,這會導致結溫升高而使帶隙電壓和內(nèi)部失調(diào)電壓降低。

圖7. ADM7172 LDO輸出電壓和輸入電壓之間的關系

直流精度

整體精度會考慮輸入電壓和負載調(diào)整率、基準電壓漂移和誤差放大器電壓漂移的影響。穩(wěn)壓電源上的輸出電壓變化主要是基準電壓源和誤差放大器的溫度變化造成的。如果使用分立電阻來設置輸出電壓,這些電阻的容差可能是影響整體精度的最主要因素。輸入電壓和負載調(diào)整率與誤差放大器失調(diào)對整體精度的影響通常為1%至3%。

例如,可利用下列工作特性來計算3.3 V LDO在0°C至125°C溫度范圍內(nèi)的總精度:電阻溫度系數(shù)為±100 ppm/°C,采樣電阻容差為±0.25%,因負載調(diào)整和輸入電壓調(diào)整而引起的輸出電壓變化分別為±10 mV和±5 mV,并且基準電壓源的精度為1%。

溫度導致的誤差 = 125°C × ±100 ppm/°C = ±1.25%

采樣電阻導致的誤差 = ±0.25%

負載調(diào)整率導致的誤差 = 100% × (±0.01 V/3.3 V) = ±0.303%

輸入電壓調(diào)整率導致的誤差 = 100% × (±0.005 V/3.3 V) = ±0.152%

基準電壓源導致的誤差 = ±1%

最差情況誤差假定所有誤差都沿同一方向變化

最差情況誤差 = ±(1.25% + 0.25% + 0.303% + 0.152% + 1%) = ±2.955%

典型誤差假定隨機變化,因此采用此誤差的平方根(rss)

典型誤差 = ± √(1.252 + 0.252 + 0.3032 + 0.1522 + 12) = ±1.655%

LDO從不會超過最差情況誤差,而rss誤差是最有可能的誤差。誤差分布會以rss誤差為中心并擴展到在尾部包括最差情況誤差。

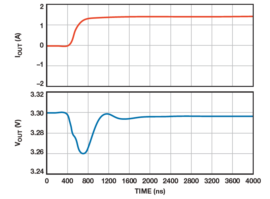

負載瞬態(tài)響應

負載瞬態(tài)響應是指負載電流階躍變化時的輸出電壓變化。它與輸出電容值、電容的等效串聯(lián)電阻(ESR)、LDO控制環(huán)路的增益帶寬以及負載電流變化的大小和速率有關。

負載瞬態(tài)的變化速率會對負載瞬態(tài)響應產(chǎn)生顯著影響。如果負載瞬態(tài)非常緩慢,比如100 mA/μs,LDO的控制環(huán)路或許能夠跟蹤該變化。但是,如果負載瞬態(tài)較快,環(huán)路無法進行補償,則可能會出現(xiàn)異常行為,例如因低相位裕量而導致過大的振鈴。

圖8顯示了ADM7172以3.75 A/μs的變化速率對1 mA至1.5 A負載瞬態(tài)的響應曲線。1.5 μs的0.1%恢復時間和最小振鈴表明其具有良好的相位裕量。

圖8. ADM7172負載瞬態(tài)響應。400 ns內(nèi)產(chǎn)生1 mA至1.5 A的負載階躍(紅線)。輸出電壓(藍線)

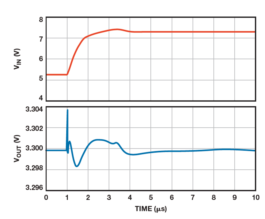

線路瞬態(tài)響應

輸入電壓瞬態(tài)響應是指輸入電壓階躍變化時的輸出電壓變化。它與LDO控制環(huán)路的增益帶寬以及輸入電壓變化的大小和速率有關。

圖9顯示了ADM7150對2 V輸入電壓階躍變化的響應。輸出電壓偏差也顯示了環(huán)路帶寬和PSRR的特性(參見下一部分)。對應于1.5 μs內(nèi)的2 V變化,輸出電壓變化約為2 mV,表明約100 kHz時PSRR約為60 dB。

同樣,跟在負載瞬態(tài)下一樣,輸入電壓的變化速率也對輸入瞬態(tài)響應有較大的影響。當輸入電壓緩慢變化(在LDO的帶寬內(nèi)只出現(xiàn)一個凹陷)時,可隱藏振鈴或其他異常行為。

圖9. ADM7150線路瞬態(tài)響應。1.5 μs內(nèi)產(chǎn)生5 V至7 V的線路階躍(紅線)。輸出電壓(藍線)

電源抑制

簡單地說,PSRR衡量電路抑制電源輸入端出現(xiàn)的外來信號(噪聲和紋波),使這些干擾信號不至于破壞電路輸出的性能。PSRR定義為:

PSRR = 20 × log(VEIN/VEOUT)

其中,VEIN和VEOUTT分別是輸入端和輸出端出現(xiàn)的外來信號。

對于ADC、DAC和放大器等電路,PSRR適用于為內(nèi)部電路供電的輸入端。對于LDO,輸入電源引腳為內(nèi)部電路供電的同時也為輸出電壓供電。PSRR具有與直流輸入電壓調(diào)整率相同的關系,但包括整個頻譜。

100 kHz至1 MHz范圍內(nèi)的電源抑制非常重要,因為LDO經(jīng)常跟高效的開關電源配合使用來為敏感的模擬電路供電。

LDO的控制環(huán)路往往是確定電源抑制性能的主要因素。同時大容量、低ESR的電容也對電源抑制性能非常有用,特別是在頻率超過控制環(huán)路增益帶寬的情況下。

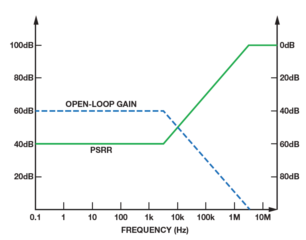

PSRR與頻率的關系

PSRR不是通過單一值來定義,因為它與頻率相關。LDO由基準電壓源、誤差放大器,以及MOSFET或雙極性晶體管等功率調(diào)整元件組成。誤差放大器提供直流增益以便調(diào)節(jié)輸出電壓。誤差放大器的交流增益特性在很大程度上決定了PSRR。典型LDO在10 Hz時可具有高達80 dB的PSRR,但在數(shù)十kHz時則可降至僅20 dB。

圖10顯示了誤差放大器的增益帶寬和PSRR之間的關系。這是一個簡化的示例,圖中忽略了輸出電容和調(diào)整元件的寄生效應。PSRR為開環(huán)增益的倒數(shù),直到3 kHz時增益開始下降為止。然后,PSRR以20 dB/十倍頻程的速率降低,直到3 MHz時達到0 dB。

圖10. LDO增益與PSRR的簡化關系圖

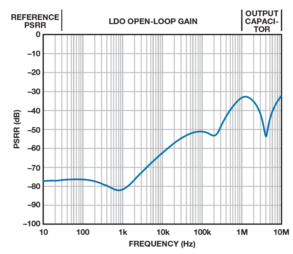

圖11顯示了用來表征LDO PSRR的三個主要頻域: 基準電壓PSRR區(qū)、開環(huán)增益區(qū)和輸出電容區(qū)。基準電壓PSRR區(qū)取決于參考放大器的PSRR和LDO的開環(huán)增益。理想情況下,參考放大器需與電源擾動完全隔離,但實際上,參考放大器只需抑制最高數(shù)十Hz的電源噪聲,因為誤差放大器反饋電路能確保在低頻時具有高PSRR。

圖11. 典型LDO PSRR與頻率的關系

在大約10 Hz以上的第二區(qū)中,PSRR主要由LDO的開環(huán)增益決定。此區(qū)中的PSRR取決于誤差放大器的增益帶寬(最高為單位增益頻率)。在低頻時,誤差放大器的交流增益等于直流增益。增益保持不變,直至達到3 dB截止頻率。在高于3 dB截止頻率下,誤差放大器的交流增益隨著頻率增加而降低,速率通常為20 dB/十倍頻程。

在誤差放大器的單位增益頻率以上,控制環(huán)路的反饋對PSRR沒有影響,此時PSRR由輸出電容和輸入與輸出電壓之間的任何寄生效應確定。在這些頻率下,PSRR主要受輸出電容的ESR,ESL以及電路板布局布線的影響。為了降低任何高頻諧振的影響,必須特別注意布局布線。

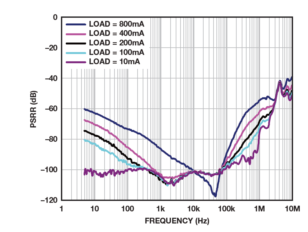

PSRR與負載電流的關系

負載電流影響誤差放大器反饋環(huán)路的增益帶寬,因此也會影響PSRR。在低負載電流下(通常小于50 mA),調(diào)整元件的輸出阻抗很高。由于控制環(huán)路的負反饋,LDO的輸出近乎是理想的電流源。輸出電容和調(diào)整元件形成的極點出現(xiàn)在相對較低的頻率,因此,PSRR在低頻條件下往往會提高。低電流時輸出級的高直流增益往往也會提高誤差放大器單位增益點以下各頻率的PSRR。

在高負載電流下,LDO輸出不能近似成一個理想電流源。調(diào)整元件的輸出阻抗會下降,從而導致輸出級的增益降低,DC至反饋環(huán)路單位增益頻率之間的PSRR會有所下降。當負載電流增加時,PSRR會急劇下降,如圖12所示。當負載電流從400 mA增加到800 mA時,ADM7150的PSRR在1 kHz時降低了20 dB。

輸出級帶寬隨輸出極點頻率的升高而增加。在高頻條件下,PSSR應會隨帶寬增加而提高,但實際上,由于總環(huán)路增益降低,高頻PSRR可能不會提高。一般而言,輕載時的PSRR優(yōu)于重載時。

圖12. ADM7150電源抑制與頻率的關系(VOUT = 5 V,VIN = 6.2 V)

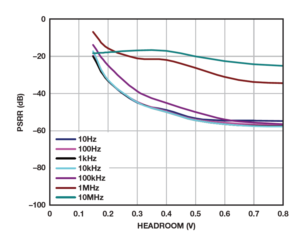

PSRR與LDO裕量的關系

PSRR也與輸入到輸出電壓差(即裕量)有關。對于固定裕量電壓,PSRR隨著負載電流的增加而降低;這在高負載電流和小裕量電壓時尤其明顯。圖13顯示了5 V ADM7172在2 A負載下PSRR與裕量電壓之間的關系差異。

隨著負載電流增加,調(diào)整元件(ADM7172的PMOSFET)脫離飽和狀態(tài),進入線性工作區(qū),其增益相應地降低。這導致LDO的總環(huán)路增益降低,因而PSRR下降。裕量電壓越小,增益降幅越大。在某些小裕量電壓下,控制環(huán)路根本沒有增益,PSRR幾乎會降至0。

導致環(huán)路增益降低的另一個因素是調(diào)整元件的非零電阻RDSON。負載電流在RDSON上引起的任何壓降都會導致調(diào)整元件有效裕量降低。例如,如果調(diào)整元件是一個1 Ω的器件,當負載電流為200 mA時,裕量將降低200 mV。當LDO在1 V或更低的裕量電壓下工作時,估算PSRR時必須考慮此壓降。

在壓差模式下,PSRR是由RDSON和輸出電容形成的極點決定的。在非常高的頻率下,PSRR會受輸出電容ESR與RDSON的比值限制。

圖13. ADM7172電源抑制與裕量的關系(VOUT = 5 V,2 A負載電流)

比較LDO PSRR規(guī)格

比較LDO的PSRR規(guī)格時,應確保測量是在相同的測試條件下進行的。許多舊式LDO僅指定120 Hz或1 kHz時的PSRR,而未提及裕量電壓或負載電流。至少,電氣技術規(guī)格表中的PSRR應針對不同的頻率列出。為使比較有意義,最好應使用不同負載和裕量電壓下的PSRR典型工作性能曲線。

輸出電容也會影響高頻時的LDO PSRR。例如,1 μF電容的阻抗是10 μF電容的10倍。在頻率高于誤差放大器的單位增益交越頻率時,電源噪聲的衰減與輸出電容有關,此時電容值就特別重要。比較PSRR數(shù)據(jù)時,輸出電容的類型和值必須相同,否則比較無效。

輸出噪聲電壓

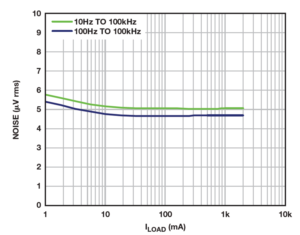

輸出噪聲電壓是指在恒定輸出電流和無紋波輸入電壓條件下,給定頻率范圍(通常為10 Hz或100 Hz至100 kHz)上的RMS輸出噪聲電壓。LDO的主要輸出噪聲源是內(nèi)部基準電壓源和誤差放大器?,F(xiàn)代LDO采用數(shù)十nA的內(nèi)部偏置電流工作,以便實現(xiàn)15 μA或更低的靜態(tài)電流。這些低偏置電流要求使用高達GΩ級的偏置電阻。輸出噪聲的典型范圍為5 μV rms至100 μV rms。圖14顯示了ADM7172輸出噪聲與負載電流之間的關系。

ADM7172等部分LDO可使用外部電阻分壓器來設置初始設定點以上的輸出電壓,使初始設定為1.2 V 的器件可提供3.6 V輸出電壓。對于這樣的應用,可向該分壓器添加降噪網(wǎng)絡,以便使輸出噪聲恢復到接近初始固定電壓的水平。

圖14. ADM7172輸出噪聲與負載電流之間的關系

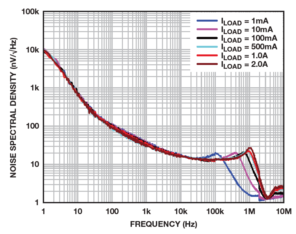

LDO輸出噪聲的另一種表示方式是噪聲頻譜密度。在寬頻率范圍內(nèi)繪制給定頻率下1 Hz帶寬上的rms噪聲曲線圖,然后使用該信息來計算給定頻率帶寬下的rms噪聲。圖15顯示了ADM7172在1 Hz到10 MHz范圍內(nèi)的噪聲頻譜密度。

圖15. ADM7172噪聲頻譜密度與負載電流之間的關系

結論

LDO看似簡單實則非常重要。若要正確運用這些LDO并獲得最佳結果,必須綜合考慮很多因素。對常用LDO術語有個基本了解后,設計工程師便可有效運用數(shù)據(jù)手冊來確定對于設計而言最為重要的參數(shù)。

參考文獻

線性穩(wěn)壓器

Ken Marasco,“如何成功運用低壓差穩(wěn)壓器”。模擬對話,第43卷第3期,2009年。

Glenn Morita和Luca Vassalli, “LDO運行窘境:低裕量和最小負載”。模擬對話,第48卷第3期,2014年。

Glenn Morita, “可調(diào)節(jié)輸出低壓差穩(wěn)壓器的降噪網(wǎng)絡”。模擬對話,第48卷第1期,2014年。Glenn Morita, “低壓差調(diào)節(jié)器——為什么選擇旁路電容很重要”。模擬對話,第45卷第1期,2011年。

Jerome Patoux, “低壓差穩(wěn)壓器”。模擬對話,第41卷第2期,2007年。

Glenn Morita于1976年獲得華盛頓州立大學電氣工程學士(BSEE)學位。畢業(yè)后加入Texas Instruments公司,期間參與研制旅行者號太空探測用紅外分光儀。之后,Glenn一直從事儀器儀表、軍用和航空航天以及醫(yī)療行業(yè)的裝置設計工作。2007年,他加入ADI公司,成為華盛頓州貝爾維尤電源管理產(chǎn)品團隊的一名應用工程師。他擁有25年以上的線性和開關模式電源設計經(jīng)驗,所設計電源的功率范圍從微瓦到千瓦不等。Glenn擁有兩項利用體熱能量給植入式心臟除顫器供電方面的專利,以及另外一項延長外部心臟除顫器電池使用壽命的專利。閑暇時,他喜歡收集礦石、雕琢寶石、攝影和逛國家公園。

Glen Morita

該作者的其他文章:

應用工程師問答—41 LDO運行窘境:低裕量和最小負載

Volume 48, Number 3第48卷第3期

評論