談談幾點避免放大器不穩(wěn)定的設計方法

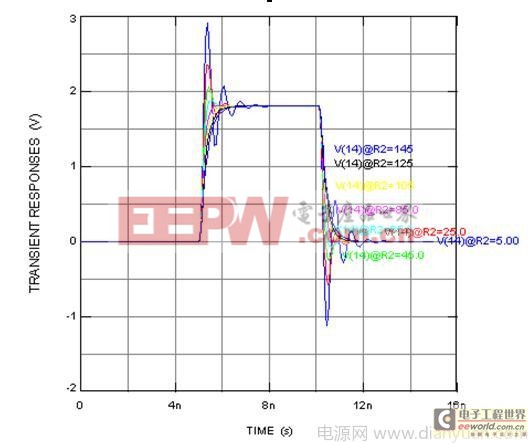

假設我們設計一個電壓跟隨器的運算放大電路, 得到的輸出波形如下圖所示, 寄生的電感, 電容產生了振蕩的可能性, 令大家都會感覺頭痛.

圖1 buffer輸出波形

輸出波形的諧波沖激到底達到什么程度才能避免振蕩呢?

這里面涉及到一點基本理論, 稍微簡單的談一下.

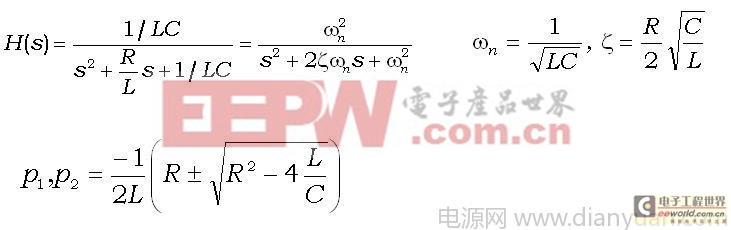

一個RLC串聯(lián)電路, 它的傳輸函數(shù)可以寫成下式表示,

其中ζ稱為damping系數(shù), ζ一般大于1的話, 這個RLC的寄生電路成分不會產生振蕩危險,但是實際中, L往往很大, 而R有往往較小, 比如layout設計的時候, 過分的把信號線設的過窄等.

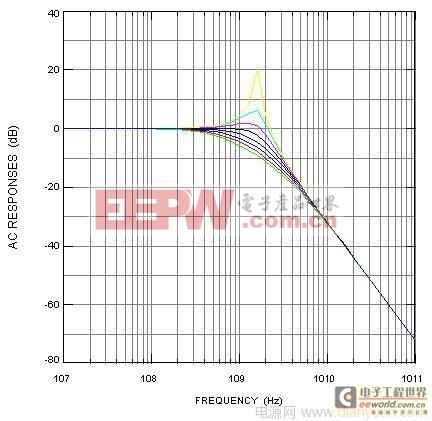

ζ如果過小,輸出信號的頻率特性在高頻處會像下圖那樣先有個沖起再下降, 所以有些電路, 設計者往往在仿真時看到的F3dB特性滿足要求, 但是實際測得的特性, 要比設計低很多, 也是因為寄生的RCL值在仿真時用的估值和實際值有一定的誤差, 而這個誤差有可能會導致Ft特性假性增加, 實質Ft要低于仿真結果不少.

圖2 電路的頻域響應

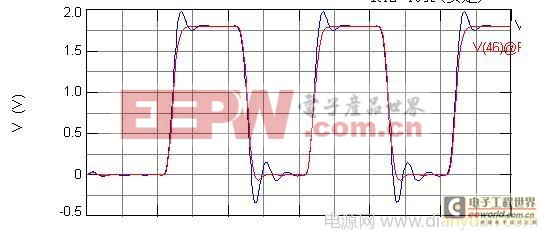

我們了解ζ的作用后, 可以在設計時避開這個危險的沖激, 如圖1, 在時域中看到的波形, 為了消除沖激, 可在電路中刻意加入一定值的電阻來增大ζ值, 使電路獲得穩(wěn)定的頻域特性.

圖3 加入串聯(lián)電阻的效果

加入一個電阻后, 可以像上圖那樣, 獲得更穩(wěn)定的時域響應波形.

如果更深一步的探討的話, 有時候加入電阻可能不能解決問題, 因為這個疊加在輸出波形的寄生沖激來自于其他地方, 比如由電路的GND線路混入, GND的不穩(wěn)定沖激可能直接疊加在輸出波形上, 這時候我們可以增加一個旁路電容, 或者把GND信號線加粗減少寄生電容等方法讓GND變得更穩(wěn)定一些.(其實也是通過ζ公式來增加C或者減小L來使ζ變得更大)

旁路電容對大家來說應該不會陌生, 一般的電路都離不開它,比如前面那一篇博客里談到的LDO設計, 往往需要在芯片外接一個數(shù)nF的電容來穩(wěn)定信號, 這里稍微提一下旁路電路的一個注意點, 雖然旁路電容可以降低低頻噪聲, 但是同時可能會引起高頻段噪聲的增加, 所以在高頻電路中同時需要加入電阻來降低寄生諧振成分的Q值. 這一點對射頻設計者來說也很重要.

評論