基于FPGA的多路脈沖重復(fù)頻率跟蹤器

2 系統(tǒng)實(shí)現(xiàn)

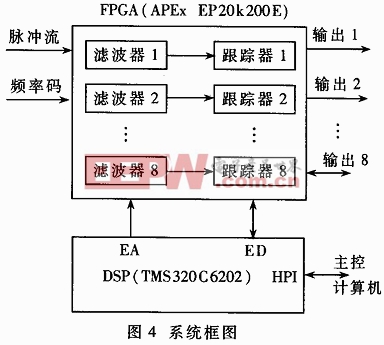

系統(tǒng)框圖如圖4所示,整個(gè)系統(tǒng)由DSP和FPGA組成,在 FPGA中設(shè)計(jì)了8路跟蹤器,最多可同時(shí)對(duì)8路信號(hào)進(jìn)行跟蹤DSP負(fù)責(zé)控制各路跟蹤器的工作,包括對(duì)各路跟蹤器裝載參數(shù)和使能,同時(shí)通過(guò)HPI(上位機(jī)接口)與彈上主控計(jì)算機(jī)傳遞數(shù)據(jù)

由于各路跟蹤器都是采用純硬件方式實(shí)現(xiàn)的,所以占用的DSP處理時(shí)間很少,DSP只需將主控計(jì)算機(jī)傳遞的信號(hào)參數(shù)裝載到跟蹤器中,并發(fā)出啟動(dòng)命令即可,余下的工作由跟蹤器自動(dòng)完成,無(wú)需DSP干預(yù),使DSP有大量的時(shí)間執(zhí)行其它計(jì)算任務(wù)

2.1 FPGA器件選擇

本設(shè)計(jì)采用Altera公司的APEX系列EP20K200EQI芯片APEX系列FPGA是Altera公司的高端產(chǎn)品,是工業(yè)界第一塊整合了SOPC(system-on-a-programmable-chip)集成電路的可編程邏輯器件其集成度高,最多能提供250萬(wàn)個(gè)門電路5萬(wàn)個(gè)邏輯單元,并且在不減少邏輯單元的情況下可提供44萬(wàn)位RAM低功耗設(shè)計(jì),采用雙電壓體系,核心電壓1.8V,I/O電壓3.3V,與多種接口標(biāo)準(zhǔn)兼容

EP20K200EQI芯片屬于工業(yè)級(jí)芯片,采用240針PQFP封裝,用戶I/O管腳數(shù)為168個(gè),提供8320個(gè)邏輯單元,芯片面積卻僅為34.5mm×34.5mm本設(shè)計(jì)中每路跟蹤器占用的邏輯單元為7%,8路跟蹤器外加一些輔助電路總共占用的邏輯單元為60%,芯片資源尚有剩余,為將來(lái)系統(tǒng)功能改進(jìn)留了余地

濾波器相關(guān)文章:濾波器原理

fpga相關(guān)文章:fpga是什么

濾波器相關(guān)文章:濾波器原理

合成孔徑雷達(dá)相關(guān)文章:合成孔徑雷達(dá)原理 脈沖點(diǎn)火器相關(guān)文章:脈沖點(diǎn)火器原理

評(píng)論