PCI局部總線簡(jiǎn)介:

PCI的含義為外部部件互連(Peripheral Component Interconnect)����。

1991年�,Intel公司對(duì)PCI局部總線進(jìn)行了定義,并與IBM�、Compaq、AST��、HP���、NEC等100多家公司聯(lián)合共謀計(jì)算機(jī)總線的發(fā)展大業(yè)�����,于是�����,PCI局部總線標(biāo)準(zhǔn)1.0版本技術(shù)規(guī)范于1992年6月22日推出���。目前�,最新的2.2修改版于1998年12月18日完成����,1999年2月發(fā)布。

PCI局部總線是一種具有多路地址線和數(shù)據(jù)線的高性能32/64位總線����。雖然在PC領(lǐng)域,PCI已經(jīng)逐漸被更高性能的PCI-Express總線替代��,但在嵌入式領(lǐng)域PCI總線依然應(yīng)用廣泛����,且其性能足夠滿足絕大多數(shù)嵌入式系統(tǒng)的需求。

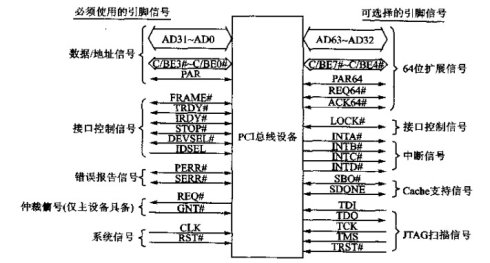

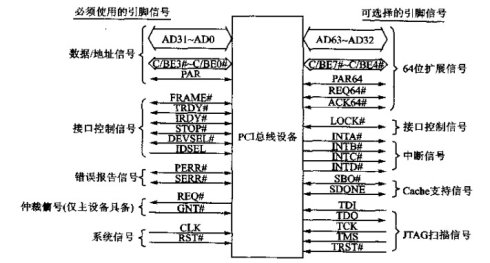

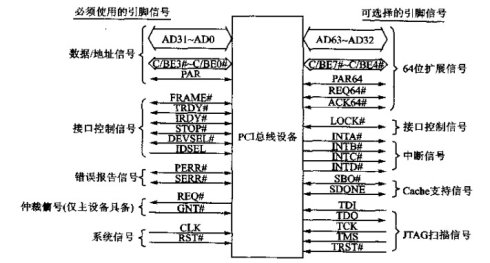

PCI總線信號(hào)定義

在一個(gè)PCI應(yīng)用系統(tǒng)中�,如果某設(shè)備取得了總線的控制權(quán),就稱其為“主設(shè)備”,而被主設(shè)備選中以進(jìn)行通信的設(shè)備稱為“從設(shè)備”或“目標(biāo)設(shè)備”�����。對(duì)于相應(yīng)的接口信號(hào)線����,通常分為必備的和可選的兩大類。如果只作為目標(biāo)設(shè)備�����,至少需要47條接口信號(hào)線����,若作為主設(shè)備,則需要49條��。下面對(duì)主設(shè)備和目標(biāo)設(shè)備綜合考慮����,并按功能分組將這些信號(hào)表示于圖中�����。

下面對(duì)PCI信號(hào)的類型規(guī)定說明:

IN 表示輸入,是標(biāo)準(zhǔn)的只作輸入的信號(hào)����。

OUT 表示輸出,是標(biāo)準(zhǔn)的圖騰柱式輸出驅(qū)動(dòng)信號(hào)��。

T/S 表示雙向的三態(tài)輸入/輸出信號(hào)�����。

O/D 表示漏極開路�����,以線或形式允許多個(gè)設(shè)備共同驅(qū)動(dòng)和分享���。

S/T/S 表示持續(xù)的并且低電平有效的三態(tài)信號(hào)�。在某一時(shí)刻只能屬于一個(gè)主設(shè)備并被其驅(qū)動(dòng)��。

系統(tǒng)信號(hào)定義:

CLK IN:對(duì)于所有的PCI設(shè)備都是輸入信號(hào)����。其頻率范圍為0~33M或者0~66M,這一頻率也稱為PCI的工作頻率�。對(duì)于PCI的信號(hào),除了RST#、INTA#~I(xiàn)NTD#之外�����,其余信號(hào)都在CLK的上升沿有效(或采樣)�。

RST# IN:復(fù)位信號(hào)。用來使PCI專用的特性寄存器�����、配置寄存器���、定時(shí)器���、主設(shè)備、目標(biāo)設(shè)備以及輸出驅(qū)動(dòng)器恢復(fù)為規(guī)定的初始狀態(tài)���。每當(dāng)復(fù)位時(shí)����,PCI的全部輸出信號(hào)一般都應(yīng)驅(qū)動(dòng)到三態(tài)�。REQ#和GNT#必須同時(shí)驅(qū)動(dòng)到三態(tài)��,不能在復(fù)位期間為高或?yàn)榈汀榉乐笰D�����、C/BE#及PAR在復(fù)位期間浮動(dòng)�,可由中央資源將它們驅(qū)動(dòng)到邏輯低,但不能驅(qū)動(dòng)為高電平�����。RST#和CLK可以不同步����,但要保證其撤銷邊沿沒有反彈。

地址和數(shù)據(jù)信號(hào):

AD[31:0] T/S:地址�、數(shù)據(jù)多路復(fù)用的輸入/輸出信號(hào)。一個(gè)總線交易由一個(gè)地址期和一個(gè)或多個(gè)數(shù)據(jù)期構(gòu)成����。在FRAME#有效時(shí),是地址期����;在IRDY#和TRDY#同時(shí)有效時(shí),是數(shù)據(jù)期���。PCI總線支持突發(fā)方式的讀寫功能����。

C/BE[3:0]# T/S:總線命令和字節(jié)使能多路復(fù)用信號(hào)線。在地址期中�,傳輸?shù)氖强偩€命令;在數(shù)據(jù)期內(nèi)�����,傳輸?shù)氖亲止?jié)使能信號(hào)�����,用來確定AD[31:0]線上哪些字節(jié)為有效數(shù)據(jù)����。C/BE[0]#應(yīng)用于字節(jié)0(最低字節(jié)),C/BE[3]#應(yīng)用于字節(jié)3(最高字節(jié))��。

PAR T/S:地址與數(shù)據(jù)位傳送時(shí)的奇偶校驗(yàn)信號(hào)����。

接口控制信號(hào):

FRAME# S/T/S:幀周期信號(hào)。由當(dāng)前的主設(shè)備驅(qū)動(dòng)�,表示當(dāng)前主設(shè)備一次交易的開始和持續(xù)時(shí)間����。FRAME#的有效預(yù)示著總線傳輸?shù)拈_始���;在FRAME#存在期間,意味著數(shù)據(jù)傳輸?shù)睦^續(xù)進(jìn)行����;FRAME#失效后,是交易的最后一個(gè)數(shù)據(jù)期�����;

IRDY# S/T/S:主設(shè)備準(zhǔn)備好信號(hào)�。由當(dāng)前主設(shè)備驅(qū)動(dòng),該信號(hào)的有效表明發(fā)起本次傳輸?shù)脑O(shè)備能夠完成交易的當(dāng)前數(shù)據(jù)期��。它要與TRDY#配合使用���,二者同時(shí)有效����,數(shù)據(jù)方能完整傳輸���。在讀周期���,該信號(hào)有效時(shí)��,表示主設(shè)備已作好接收數(shù)據(jù)的準(zhǔn)備��。在寫周期�����,該信號(hào)有效時(shí)���,表明數(shù)據(jù)已提交到AD總線上。如果IRDY#和TRDY#有一個(gè)無(wú)效��,將插入等待周期�����。

TRDY# S/T/S:目標(biāo)設(shè)備準(zhǔn)備好信號(hào)�����。由當(dāng)前被尋址的目標(biāo)設(shè)備驅(qū)動(dòng)����,該信號(hào)有效表示目標(biāo)設(shè)備已經(jīng)作好完成當(dāng)前數(shù)據(jù)傳輸?shù)臏?zhǔn)備工作�。同樣���,該信號(hào)要與IRDY#配合使用,二者同時(shí)有效���,數(shù)據(jù)方能完整傳輸���。在寫周期,該信號(hào)有效�����,表示從設(shè)備已作好接收數(shù)據(jù)的準(zhǔn)備��;在讀周期���,該信號(hào)有效�����,表明數(shù)據(jù)已提交到AD總線上�。同理,TRDY#和 IRDY#任一個(gè)無(wú)效�����,都將插入等待周期��;

STOP# S/T/S:停止數(shù)據(jù)傳送信號(hào)�。由目標(biāo)設(shè)備驅(qū)動(dòng)。當(dāng)該信號(hào)有效時(shí)�,表示目標(biāo)設(shè)備要求主設(shè)備中止當(dāng)前的數(shù)據(jù)傳送。

IDSEL# IN:初始化設(shè)備選擇信號(hào)��。在參數(shù)配置讀和配置寫期間���,用作片選信號(hào)�。

DEVSEL# S/T/S:設(shè)備選擇信號(hào)�。該信號(hào)有效時(shí),表示驅(qū)動(dòng)它的設(shè)備已稱為當(dāng)前訪問的目標(biāo)設(shè)備�����。換言之����,該信號(hào)的有效說明總線上某一設(shè)備已被選中����。如果一個(gè)主設(shè)備啟動(dòng)一個(gè)交易并且在6個(gè)CLK周期內(nèi)沒有檢測(cè)到DEVSEL#有效��,它必須假定目標(biāo)設(shè)備沒有反應(yīng)或者地址不存在�����,從而實(shí)施主設(shè)備缺省�。

LOCK# S/T/S:鎖定信號(hào)(可選)�����。當(dāng)該信號(hào)有效時(shí)�����,表示對(duì)橋的原始操作可能需要多個(gè)傳輸才能完成���,也就是說��,對(duì)此設(shè)備的操作是排它性的���。鎖定只能由主橋����、PCI-PCI橋和擴(kuò)展總線橋發(fā)起�����。

仲裁信號(hào):

REQ# T/S:總線占用請(qǐng)求信號(hào)���。該信號(hào)一旦有效即表明驅(qū)動(dòng)它的設(shè)備向仲裁器要求使用總線����。它是一個(gè)點(diǎn)到點(diǎn)的信號(hào)線�����,任何主設(shè)備都有其REQ#信號(hào)��。當(dāng)RST#有效時(shí)�����,REQ#必須為三態(tài)��。

GNT# T/S:總線占用允許信號(hào)。用來向申請(qǐng)總線占用的設(shè)備表示其請(qǐng)求已獲得批準(zhǔn)���。這也是一個(gè)點(diǎn)到點(diǎn)的信號(hào)線����,任何主設(shè)備都有自己的GNT#信號(hào)�。當(dāng)RST#有效時(shí),必須忽略GNT#���。

每一個(gè)PCI主設(shè)備都有一對(duì)仲裁線直接連接到PCI仲裁器上����。當(dāng)一個(gè)主設(shè)備請(qǐng)求使用總線時(shí)�����,它會(huì)使連接到仲裁器上的REQ#有效��,當(dāng)仲裁器決定正在請(qǐng)求的主設(shè)備應(yīng)該授權(quán)控制總線時(shí)�,它會(huì)使對(duì)應(yīng)的GNT#有效���。在PCI環(huán)境中��,總線仲裁器在同時(shí)有另一個(gè)主設(shè)備仍控制總線時(shí)起作用����,這稱為“隱式”仲裁。當(dāng)主設(shè)備接受來自仲裁器的授權(quán)時(shí)���,必須等待當(dāng)前的主設(shè)備完成其傳送�,直到采樣到FRAME#和IRDY#均無(wú)效時(shí)��,它才認(rèn)為自己取得總線授權(quán)�。

錯(cuò)誤報(bào)告信號(hào):

PERR# S/T/S:數(shù)據(jù)奇偶校驗(yàn)錯(cuò)誤信號(hào);由數(shù)據(jù)的接收端驅(qū)動(dòng)�����,同時(shí)設(shè)置其狀態(tài)寄存器中的奇偶校驗(yàn)錯(cuò)誤位�����。一個(gè)交易的主設(shè)備負(fù)責(zé)給軟件報(bào)告奇偶校驗(yàn)錯(cuò)誤�,為此在寫數(shù)據(jù)期它必須檢測(cè)PERR信號(hào)。

SERR# O/D:系統(tǒng)錯(cuò)誤報(bào)告信號(hào)���;它的作用是報(bào)告地址奇偶錯(cuò)誤���,特殊周期命令的數(shù)據(jù)錯(cuò)誤�����。SERR#是一個(gè)OD(漏極開路)信號(hào)����,它通常會(huì)引起一個(gè)NMI中斷�,Power PC中會(huì)引起機(jī)器核查中斷。

中斷信號(hào):

中斷在PCI中是可選項(xiàng)��,屬于電平敏感型�����,低電平有效��,OD�����,與時(shí)鐘異步����。其中INTB ~I(xiàn)NTD只能用于多功能設(shè)備。中斷線和功能之間的最終對(duì)應(yīng)關(guān)系是由中斷引腳寄存器來定義的����。

附加信號(hào):

PRSNT[2:1]:插卡存在信號(hào);用于指出PCI插件板上是否存在插卡板����,如存在則要求母板為其供電;

CLKRUN:時(shí)鐘運(yùn)行信號(hào)���;用于停止或者減慢CLK�;

M66EN:66M使能信號(hào)����;

PME#:電源管理事件信號(hào)。

3.3Vaux:輔助電源信號(hào)���;當(dāng)插卡主電源被軟件關(guān)閉時(shí)�����,3.3Vaux為插件提供電能以產(chǎn)生電源管理事件�。

64位總線擴(kuò)展信號(hào):

AD[64:32]:在地址期���,如使用DAC命令且REQ64有效時(shí)為高32位地址���;在數(shù)據(jù)期����,REQ64和ACK64都有效時(shí)高32位數(shù)據(jù)有效�����。

C/BE[7:4]:用法與AD信號(hào)同���。

REQ64#:64位傳輸請(qǐng)求�����;由主設(shè)備驅(qū)動(dòng)��,并和FRAME有相同的時(shí)序���;

ACK64#:64位傳輸認(rèn)可;由從設(shè)備驅(qū)動(dòng)��,并和DEVSEL有相同的時(shí)序����;

PAR64#:奇偶雙字節(jié)校驗(yàn)。

JTAG/邊界掃描信號(hào):

TCK���,TDI����,TDO����,TMS,TRST#

評(píng)論