基于DSP_FPGA的高速數(shù)字信號處理平臺的電源設(shè)計(jì)

摘要

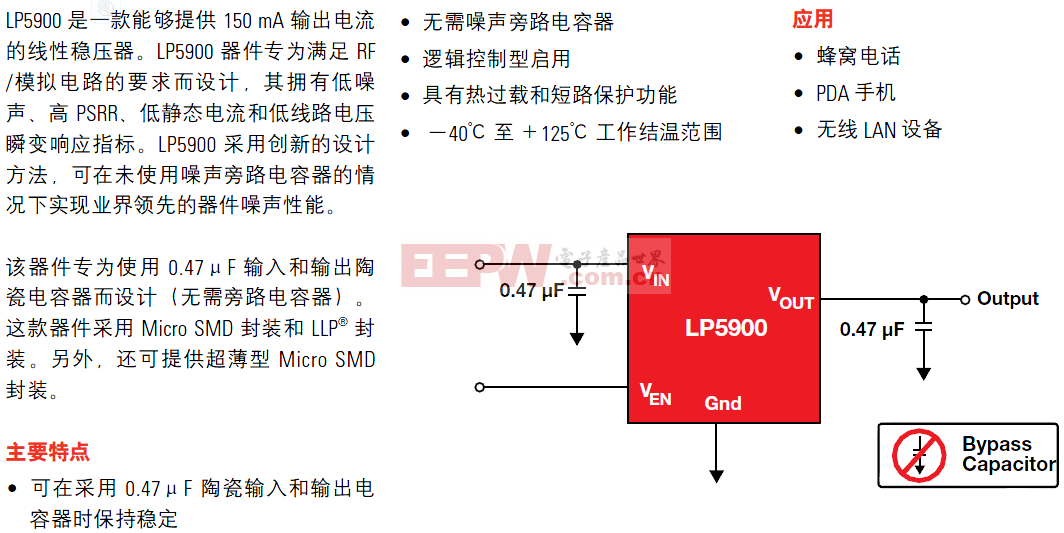

本文引用地址:http://m.butianyuan.cn/article/201808/386373.htm研究了DSP+FPGA高速數(shù)字信號處理器系統(tǒng)電源的供電需求, 采用了開關(guān)電源和線性穩(wěn)壓電源的混合電源系統(tǒng),解決了高速數(shù)字信號處理器系統(tǒng)電源的供電問題.經(jīng)實(shí)際的測試驗(yàn)證表明設(shè)計(jì)的該系統(tǒng)電源滿足各個(gè)高速處理模塊 的供電需求,也表明該系統(tǒng)電源的突出優(yōu)點(diǎn)是供電電源的高穩(wěn)定性.

評論