用于PDIC的跨阻放大器的優(yōu)化設(shè)計(jì)

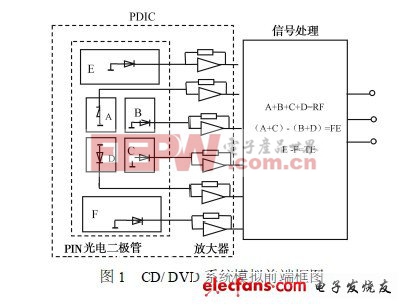

提出了一種用于PDIC 的跨阻放大器。電路由三級(jí)相同的推挽放大器級(jí)聯(lián)而成,每級(jí)均采用一動(dòng)態(tài)電阻對(duì)負(fù)載進(jìn)行補(bǔ)償,以提高放大器的相位裕度。反饋電阻由一柵極受控的PMOS 管替代,避免了大尺寸多晶硅電阻引入的附加相移,增加了電路的穩(wěn)定性。采用XFAB 0. 6μm CMOS 工藝提供的PD K,在Cadence Spect re 環(huán)境下進(jìn)行電路設(shè)計(jì)、仿真驗(yàn)證。仿真結(jié)果表明,電路的增益、帶寬及穩(wěn)定性均得到滿意結(jié)果。

電子管相關(guān)文章:電子管原理

評(píng)論