利用FPGA實(shí)現(xiàn)優(yōu)異的家用電器設(shè)計(jì)

1. 維持電壓恒定;

2. 盡量減少相位不平衡;

3. 維持功率因數(shù)恒定;

4. 保持良好的電源質(zhì)量;

5. 采用可調(diào)式速度驅(qū)動(dòng)或雙速電機(jī);

6. 控制好溫度;

7. 匹配電機(jī)運(yùn)行速度。

利用數(shù)字電路或FPGA控制模擬電機(jī)電路將使系統(tǒng)成本和功耗大大降低。采用FPGA除了可以節(jié)能之外,還能夠?qū)⑶度胧綌?shù)字信號(hào)處理(DSP)、微控制器、I/O接口等功能整合到一起,從而實(shí)現(xiàn)完整的家電設(shè)計(jì)。

脈沖寬度調(diào)制

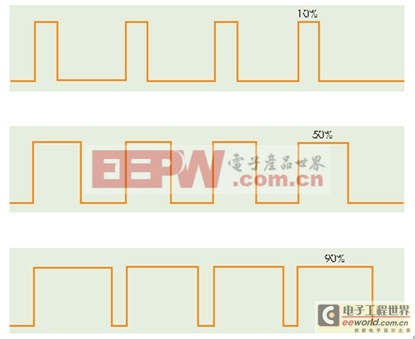

用數(shù)字方式控制模擬電機(jī)電路的一種典型方法是采用脈沖寬度調(diào)制(PWM)。此時(shí)方波的時(shí)間周期是恒定的,而接通時(shí)間(TON)即信號(hào)保持高電平的時(shí)間可以被改變或調(diào)制。因此,信號(hào)的占空比或平均直流電平是變化的。借助于數(shù)字系統(tǒng)的支持,PWM已經(jīng)成為控制模擬電路的一種極好方式。圖1就是數(shù)字脈沖的接通時(shí)間改變的例子。

應(yīng)用實(shí)例包括電壓調(diào)整,即通過改變占空比將輸出電壓控制到所要求的電平。另一個(gè)例子是功率發(fā)送,這時(shí)的平均發(fā)送功率是調(diào)制占空比的函數(shù)。PWM的實(shí)現(xiàn)取決于具體的使用方法,對(duì)于簡(jiǎn)單的電壓調(diào)整,可以使用CPLD(例如Altera MAX II)實(shí)現(xiàn),而對(duì)于需要利用內(nèi)部DSP模塊的復(fù)雜控制算法,可以使用低成本的FPGA(例如Altera Cyclone III)實(shí)現(xiàn)。

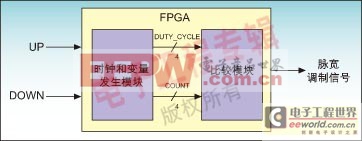

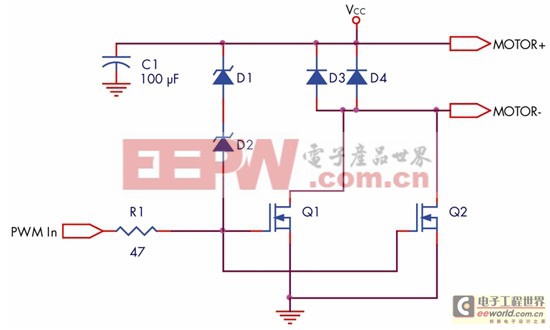

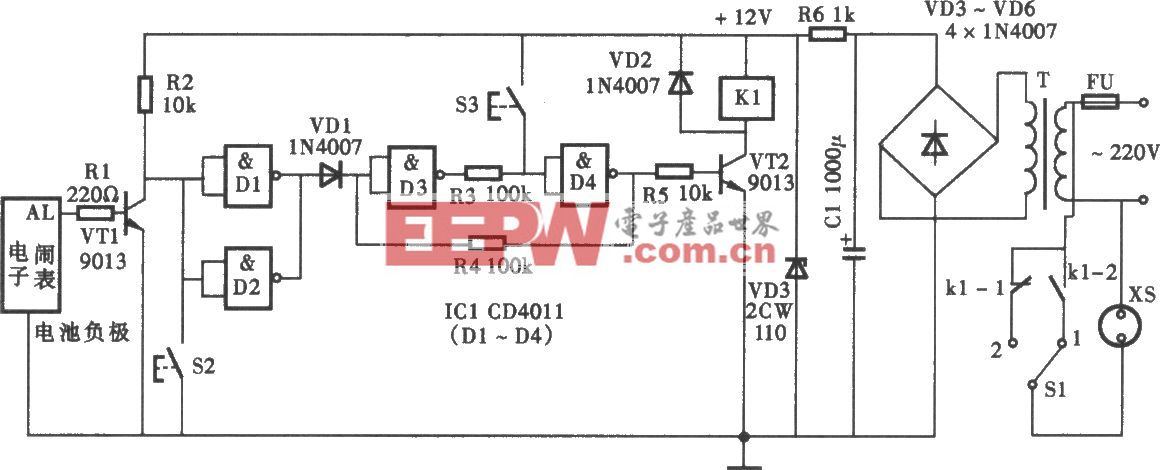

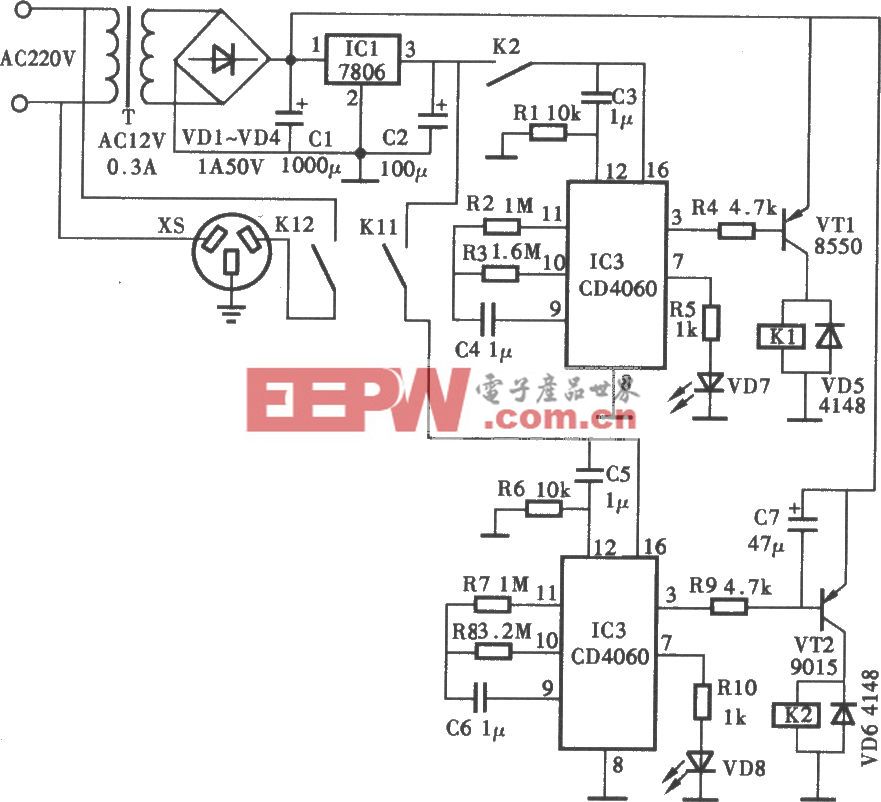

圖2是PWM的基本方框圖,而圖3則是一個(gè)驅(qū)動(dòng)模擬電機(jī)接口電路的調(diào)制輸出。UP和DOWN輸入信號(hào)被用來調(diào)整輸出信號(hào)的占空比,它們可以由微控制器產(chǎn)生。第一個(gè)模塊利用所有MAX II器件中都有的UFM振蕩器來產(chǎn)生兩個(gè)頻率不同的時(shí)鐘。來自該模塊的4位輸出信號(hào)DUTY_CYCLE的增加或降低取決于UP或DOWN信號(hào)的證實(shí)。第二個(gè)4位輸出信號(hào)COUNT以第一個(gè)模塊中產(chǎn)生的較高時(shí)鐘頻率連續(xù)增加。該信號(hào)與第二個(gè)模塊中相同頻率的DUTY_CYCLE信號(hào)進(jìn)行比較。比較的結(jié)果是分配到最終輸出信號(hào)PWM的單個(gè)位。信號(hào)DUTY_CYCLE是一個(gè)4位的變量,因此輸出信號(hào)的占空比具有16個(gè)不同的取值。在本設(shè)計(jì)實(shí)現(xiàn)中,輸入U(xiǎn)P的優(yōu)先級(jí)要高于DOWN。因此,如果兩個(gè)信號(hào)同時(shí)為高電平,輸出信號(hào)將被視作占空比的增加。

圖1:PWM波形示例。

圖2:PWM基本框圖

圖3:電機(jī)模擬驅(qū)動(dòng)電路

相關(guān)推薦

技術(shù)專區(qū)

- FPGA

- DSP

- MCU

- 示波器

- 步進(jìn)電機(jī)

- Zigbee

- LabVIEW

- Arduino

- RFID

- NFC

- STM32

- Protel

- GPS

- MSP430

- Multisim

- 濾波器

- CAN總線

- 開關(guān)電源

- 單片機(jī)

- PCB

- USB

- ARM

- CPLD

- 連接器

- MEMS

- CMOS

- MIPS

- EMC

- EDA

- ROM

- 陀螺儀

- VHDL

- 比較器

- Verilog

- 穩(wěn)壓電源

- RAM

- AVR

- 傳感器

- 可控硅

- IGBT

- 嵌入式開發(fā)

- 逆變器

- Quartus

- RS-232

- Cyclone

- 電位器

- 電機(jī)控制

- 藍(lán)牙

- PLC

- PWM

- 汽車電子

- 轉(zhuǎn)換器

- 電源管理

- 信號(hào)放大器

評(píng)論