電源設(shè)計小貼士46:正確地同步降壓FET時序

由于工程師們都在竭盡所能地獲得其電源的最高效率,時序優(yōu)化正變得越來越重要。在開關(guān)期間,存在兩個過渡階段:低壓側(cè)開關(guān)開啟和高壓側(cè)開關(guān)開啟。

低壓側(cè)開啟開關(guān)至關(guān)重要,因為該過渡階段幾乎沒有損耗,也即“無損開啟”。在高壓側(cè)開關(guān)關(guān)閉以后,電感電流驅(qū)動開關(guān)節(jié)點電壓無損接地。開啟低壓側(cè)開關(guān)的最佳時機便為過渡結(jié)束時。如果在低壓側(cè)開啟以前主體二極管短暫導(dǎo)電,則其無關(guān)緊要,因為它不會導(dǎo)致反向恢復(fù)損耗。在下一個開關(guān)過渡之前,該結(jié)點處的過剩載流全部耗散。但是,如果電流仍然長時間存在于主體二極管內(nèi),則會有過高的傳導(dǎo)損耗。高壓側(cè) FET 開啟時序是最為重要的過渡。由于同低壓側(cè) FET 存在交叉導(dǎo)通,因此開啟過早會導(dǎo)致直通損耗;開啟過晚又會導(dǎo)致傳導(dǎo)損耗增高,并且會將過剩載流注入低壓側(cè) FET 主體二極管內(nèi)(必須對其進行恢復(fù))。不管哪種情況,都會降低效率。

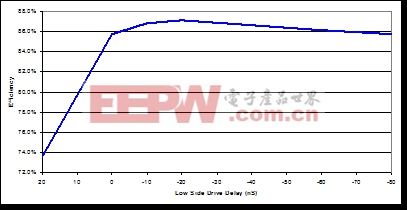

為了說明效率與驅(qū)動信號之間時序的關(guān)系,我構(gòu)建起了一些具有驅(qū)動器信號可調(diào)節(jié)延遲的電源。之后,我比較了效率與延遲時間,對其存在的關(guān)系進行了研究。圖 1A-1C 顯示了結(jié)果。

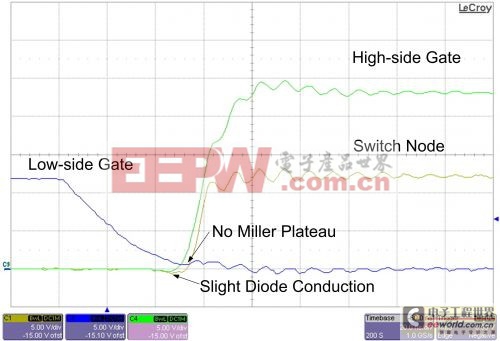

圖 1A 顯示了當高壓側(cè) FET 在低壓側(cè) FET 完全關(guān)閉之前開啟時的情況。在低壓側(cè)柵極驅(qū)動中有一個明顯的更大的Miller 區(qū)域,其低壓側(cè) FET 和高壓側(cè) FET 同時導(dǎo)通,從而在功率級中產(chǎn)生直通電流。當?shù)蛪簜?cè) FET 最終關(guān)閉時,在開關(guān)節(jié)點處存在額外的電壓過沖。在圖 1B 中,在低壓側(cè) FET 關(guān)閉且主體二極管中形成電流以后,高壓側(cè) FET 才開啟。當高壓側(cè) FET 開啟時,其恢復(fù)該主體二極管,并且會有一個電流峰值讓開關(guān)節(jié)點電壓出現(xiàn)振鈴。但是,由于所用MOSFET體二極管的反向恢復(fù)時間(12 nS)極短,因此這種現(xiàn)象并不明顯。主體二極管速度越慢,振鈴越明顯。圖 1C 擁有最高的電源效率。在高壓側(cè)開關(guān)開啟以前,低壓側(cè)柵極電壓降至接地電壓附近。高壓側(cè)在更低的主體二極管導(dǎo)電以前開啟,開關(guān)節(jié)點振鈴最小化。

圖 1A 先進的高壓側(cè)時序產(chǎn)生直通電流

圖 1B 高壓側(cè)驅(qū)動延遲時主體二極管導(dǎo)電

圖 1C 最佳時序帶來更高的效率和更低的應(yīng)力

圖 2 顯示了不同柵極驅(qū)動時序情況下 12 伏到 1 伏/15 安培、300 kHz 功率級的效率曲線??潭茸髠?cè)代表高壓側(cè)開關(guān)提前開啟,如圖 1A 所示。右側(cè)代表一個經(jīng)過延遲的高壓側(cè)柵極驅(qū)動(圖 1B)。在左邊,效率急劇下降,原因是功率級的直通電流損耗。在右邊,效率逐漸下降。

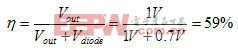

效率逐漸下降的原因有兩個:來自低壓側(cè) FET 主體二極管的傳導(dǎo)損耗和反向恢復(fù)損耗。在主體二極管導(dǎo)電期間,主體二極管電壓下降約 0.7伏。方程式 1 表示了主體二極管導(dǎo)電期間的最大電源效率,其大致如下:

方程式1

方程式1如果主體二極管在 3us 時間中有 50ns 時間導(dǎo)電,則可對總效率產(chǎn)生約 1.2% 的影響。就該功率級而言,反向恢復(fù)損耗微不足道,原因是使用了 12 nS 短反向恢復(fù)時間的 MOSFET。

圖 2 驅(qū)動器時序可極大影響效率

總之,同步降壓穩(wěn)壓器中正確的柵極驅(qū)動信號時序,對于最大化效率至關(guān)重要。這種時序可最小化低壓側(cè) FET 主體二極管導(dǎo)電時間。高壓側(cè) FET 開啟是最為關(guān)鍵的過渡階段,同時應(yīng)避免在低壓側(cè)完全關(guān)閉以前開啟高壓側(cè) FET。這樣做可以最小化開關(guān)損耗,并減少過渡期間的電壓振鈴。

更多詳情,請參閱 2003 年 4 月 TI《應(yīng)用手冊》(SLUA281)文章《柵極驅(qū)動升壓同步 DC/DC 功率轉(zhuǎn)換器效率預(yù)測》

評論