ARM寄存器詳解

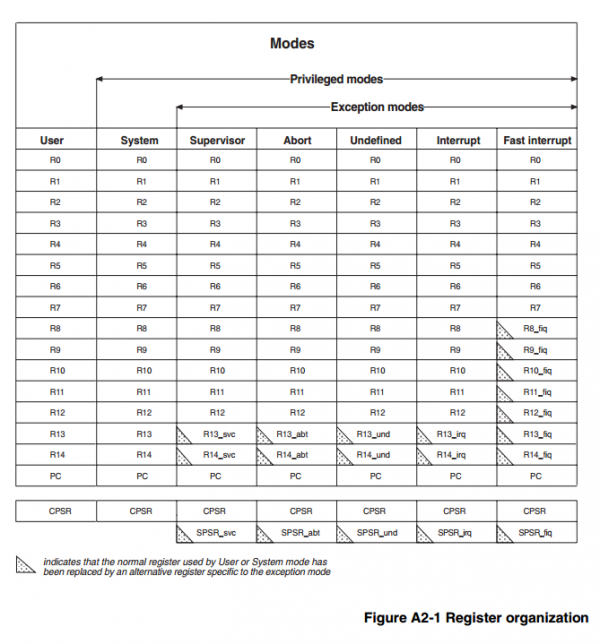

1. 31個(gè)通用寄存器

本文引用地址:http://m.butianyuan.cn/article/201611/318751.htm2. 6個(gè)狀態(tài)寄存器

R13作為堆棧指針

R14鏈接寄存器

1.保存函數(shù)返回地址

2. 異常返回地址

R15程序計(jì)數(shù)器(PC指針)

程序狀態(tài)寄存器

只有在異常時(shí)才有程序狀態(tài)寄存器

為什么有兩個(gè)CPSR

SPSR當(dāng)異常發(fā)生時(shí)保存CPSR的地址

當(dāng)異常結(jié)束時(shí)SPSR將之前保存的地址給CPSR

程序狀態(tài)寄存器的數(shù)據(jù)格式

NIs set to bit 31 of the result of the instruction. If this result is regarded as a twos complement

signed integer, then N = 1 if the result is negative and N = 0 if it is positive or zero.

ZIs set to 1 if the result of the instruction is zero (this often indicates anequalresult from a

comparison), and to 0 otherwise.

I bit Disables IRQ interrupts when it is set.

F bitDisables FIQ interrupts when it is set.

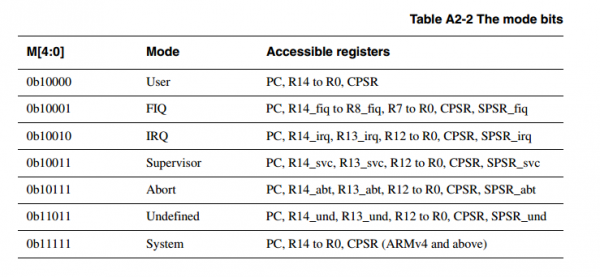

M 標(biāo)識處理器的工作模式

獲取和設(shè)置工作模式

評論