基于FPGA實現(xiàn)感性元件電阻測試

引言:

本文引用地址:http://m.butianyuan.cn/article/201701/337463.htm近期給汽車電子某廠商做了一套點火線圈測試系統(tǒng),有一部分是關(guān)于感性線圈電阻測試,具體要求如下:初級電阻 620 mΩ +-50mΩ、次級電阻 9.5 kΩ +-0.9 kΩ、導(dǎo)線電阻 150 mΩ +-50 mΩ。

一、挑戰(zhàn):

初級線圈電阻較?。╩Ω級),測量過程中還要考慮導(dǎo)線電阻影響;而次級電阻大(k Ω級),用DMM數(shù)字萬用表進行測試是不錯的方案,但是由于測試設(shè)備是放在生產(chǎn)線上,對體積、功耗和可靠性要求很高,NI CompactRIO平臺是非常好的選擇,但是NI CompactRIO電阻測試模塊量程大,不適合小電阻測試。并且由于被測件是感性線圈,通過恒電流激勵4線制測電阻方式,由于恒電流激勵穩(wěn)定性問題,會 使得感性線圈產(chǎn)生感應(yīng)電動勢,對小電阻測試帶來考驗。

二、方案:

選用NI 9265電流輸出模塊作為電阻測試激勵,通過4線制來測量電壓方式來進行電阻測試。為了減小電流激勵不穩(wěn)定性導(dǎo)致感應(yīng)電動勢產(chǎn)生,帶來測量誤差的影響,通過在FPGA用高頻(10k)采樣,然后降采樣到低頻(50-100Hz)模式,濾除感應(yīng)線圈電動勢的影響。

三、具體實施:

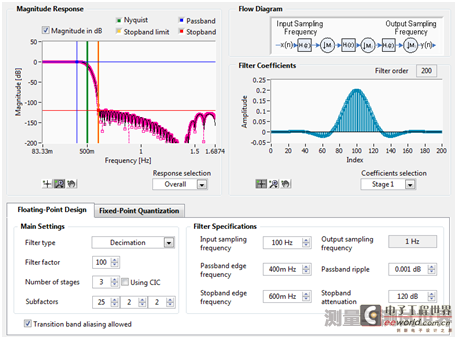

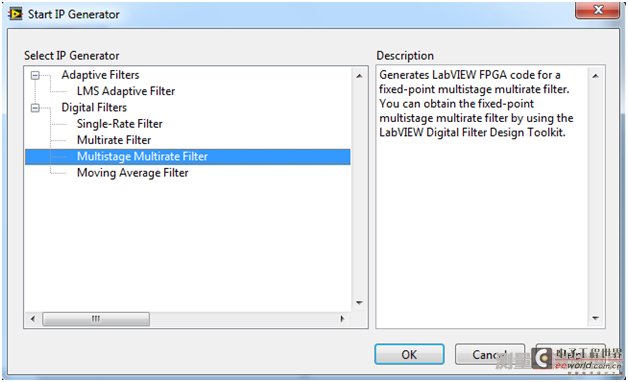

1、 構(gòu)造浮點濾波器:在DFD設(shè)計工具包選擇Multistage Decimation Filter

圖1、DFD構(gòu)造多級降采樣浮點濾波器

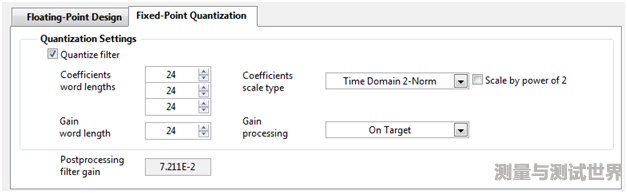

2、 多級降采樣定點濾波器設(shè)計

圖2、浮點濾波器量化構(gòu)造定點濾波器

3、 多級降采樣定點濾波器FPGA實現(xiàn)

關(guān)鍵詞:

FPGA感性元件電阻測

評論