基于FPGA的脈沖重復頻率(PRF)跟蹤器的設計

隨著高科技的迅速發(fā)展,現(xiàn)代戰(zhàn)爭已經(jīng)不僅是傳統(tǒng)意義戰(zhàn)場上的較量,電子戰(zhàn)已經(jīng)成為決定戰(zhàn)爭勝負的重要因素之一?反輻射導彈在電子戰(zhàn)中扮演著重要的角色,它在戰(zhàn)爭中可以有效地壓制或摧毀敵方武器系統(tǒng)中的雷達,使敵方武器系統(tǒng)失去攻擊能力,取得制空權,發(fā)揮己方的空中優(yōu)勢?在反輻射導彈中引導攻擊目標的是雷達導引頭,它截獲目標雷達的信號并檢測出信號入射角,輸送給導彈控制系統(tǒng),導引導彈跟蹤目標直到命中?

脈沖重復頻率(PRF)跟蹤器是雷達導引頭的重要器件,它的功能是在雷達導引頭接收到的信號流中選擇出目標信號?在日趨復雜的電磁環(huán)境下,空間信號密度已經(jīng)達到50~100萬脈沖/秒,至少相當于幾百個輻射源的總和?所以信號接收機截獲到的信號通常是不止一部雷達的信號,往往包括很多部?脈沖重復頻率跟蹤器就是要在包含多部雷達的信號流中選出要截獲的那部雷達信號,送到后面的信號處理機?如圖1所示,接收機收到的信號包括多部信號,經(jīng)過脈沖重復頻率跟蹤器的選擇后只輸出一部信號送到后續(xù)的信號處理機? 目前,實現(xiàn)脈沖重復頻率跟蹤器的方法主要有三種:純軟方式?半軟半硬方式和純硬方式?純軟方式用高速DSP完成全部功能,這種方式在現(xiàn)代密集信號環(huán)境下將影響系統(tǒng)的實時性,要想實現(xiàn)多路信號的跟蹤需要多個DSP,這將造成系統(tǒng)體積龐大?半軟半硬方式用DSP和硬件電路分別完成一部分功能,和前一種方式有相同的缺點?純硬方式用FPGA或CPLD實現(xiàn)跟蹤信號的全部功能,具有實時性好?性能穩(wěn)定的優(yōu)點,能滿足目前復雜電磁環(huán)境的要求,并且集成度高,可以實現(xiàn)系統(tǒng)的小型化?

本文利用FPGA資源豐富?易于編程的特點設計了純硬方式的脈沖重復頻率跟蹤器,實現(xiàn)了在密集信號環(huán)境下的信號跟蹤,并且將多路并行的跟蹤器集成在一片FPGA中,簡化了系統(tǒng)結(jié)構(gòu),縮小了體積?

1 脈沖重復頻率(PRF)跟蹤器原理

1.1 脈沖重復頻率跟蹤器

為了在密集的信號流中分離出一部信號,需要知道該信號的脈沖重復頻率以及脈沖重復周期(PRI)類型,這部分工作通常由雷達偵察系統(tǒng)或反輻射導彈的信號預處理器來完成?脈沖重復頻率是識別雷達的一個重要參數(shù),因為它是雷達最具特征的信號參數(shù)?所說的最具特征,是指雷達的性能受其所使用的脈沖重復頻率的影響很大,例如對于常規(guī)雷達來說,脈沖重復頻率的數(shù)值決定了雷達的最大無模糊距離和最大無模糊徑向速度?脈沖重復周期(PRI)是脈沖重復頻率的倒數(shù),其類型大致可分為三種:固定?跳變和參差?固定PRI信號的各個脈沖之間的間隔是恒定的;如果把信號的PRI加上人為的隨機跳變就構(gòu)成了跳變PRI信號,其PRI的變化值可達脈沖重復周期平均值的15%;參差PRI信號由多個間隔不同的脈沖組成一個信號序列幀,各脈沖重復周期的總和稱為幀周期,幀周期之間的小間隔稱為小周期,一般幀周期是固定的?

根據(jù)以上分析,為了實現(xiàn)各種PRI類型信號的實時跟蹤,在FPGA中設計了脈沖重復頻率跟蹤器電路,其原理圖如圖2所示?

由圖2可見,跟蹤器包括重復周期寄存器0~7?參差寄存器?輸出波門寄存器以及重復周期計數(shù)器?輸出波門計數(shù)器?輸出控制器等單元?其中,參差寄存器存儲參差PRI信號的小周期數(shù),即參差數(shù);重復周期寄存器0~7存儲信號的各個重復周期?由于目前參差雷達一般不超過8參差數(shù),所以重復周期寄存器有8個即可,參差寄存器儲存的參差數(shù)控制各個重復周期寄存器?例如參差數(shù)等于3,則只有0~2號重復周期寄存器有效,其余5個無用?若參差數(shù)等于1,則只有0號重復周期寄存器有效,這相當于固定PRI信號的情況?輸出波門寄存器存儲的是波門寬度,其值主要由跳變PRI信號的變化量決定?若變化量大,則輸出波門寬度也要大,這樣才能選中要截獲的信號?數(shù)值關系可表示為:波門寬度=PRI變化量+脈沖寬度+常量A?常量A為調(diào)整參數(shù),可根據(jù)調(diào)試情況決定?重復周期計數(shù)器是跟蹤器的核心器件,它根據(jù)信號脈沖的到達與否決定何時開始計數(shù),計數(shù)周期是重復周期寄存器中的值,各個有效的重復周期寄存器的存儲值循環(huán)采用?其輸出送到輸出波門計數(shù)器,后者根據(jù)輸出波門寄存器中的值確定波門的寬度?輸出控制器是主要的邏輯控制單元,控制整個跟蹤器的工作?輸出控制器的功能還包括判斷信號是否截獲成功?信號是否丟失等?

1.2 信號濾波器

各種電子對抗設備數(shù)目的急劇增加使雷達導引頭系統(tǒng)處于高度密集的信號環(huán)境中,脈沖重復頻率跟蹤器的實時性受到考驗?基于以上考慮,在跟蹤器的前端設計了信號濾波器,對信號脈沖流進行稀釋,減輕跟蹤器的壓力?信號濾波器的原理圖如圖3所示?

信號濾波器的核心是關聯(lián)比較器,FPGA為關聯(lián)比較器的實現(xiàn)提供了便利條件?本系統(tǒng)中采用了兩路關聯(lián)比較器,一路用于信號載頻濾波,一路用于信號脈寬濾波?由圖3可見,只有載頻和脈寬都在一定的范圍之內(nèi)的信號才能通過濾波器,即對信號進行了篩選?在現(xiàn)代復雜電磁環(huán)境下,載頻和脈寬都比較接近的信號是相當多的,同時比較器的上?下限不能取得過于接近,這樣濾波器的輸出就不只限于一部信號,即使這樣也極大地稀釋了信號流?這種稀釋過的信號流送到跟蹤器,有助于提高跟蹤器的實時性,更利于成功地截獲信號?

2 系統(tǒng)實現(xiàn)

系統(tǒng)框圖如圖4所示,整個系統(tǒng)由DSP和FPGA組成,在 FPGA中設計了8路跟蹤器,最多可同時對8路信號進行跟蹤?DSP負責控制各路跟蹤器的工作,包括對各路跟蹤器裝載參數(shù)和使能,同時通過HPI(上位機接口)與彈上主控計算機傳遞數(shù)據(jù)?

由于各路跟蹤器都是采用純硬件方式實現(xiàn)的,所以占用的DSP處理時間很少,DSP只需將主控計算機傳遞的信號參數(shù)裝載到跟蹤器中,并發(fā)出啟動命令即可,余下的工作由跟蹤器自動完成,無需DSP干預,使DSP有大量的時間執(zhí)行其它計算任務?

2.1 FPGA器件選擇

本設計采用Altera公司的APEX系列EP20K200EQI芯片?APEX系列FPGA是Altera公司的高端產(chǎn)品,是工業(yè)界第一塊整合了SOPC(system-on-a-programmable-chip)集成電路的可編程邏輯器件?其集成度高,最多能提供250萬個門電路?5萬個邏輯單元,并且在不減少邏輯單元的情況下可提供44萬位RAM?低功耗設計,采用雙電壓體系,核心電壓1.8V,I/O電壓3.3V,與多種接口標準兼容?

EP20K200EQI芯片屬于工業(yè)級芯片,采用240針PQFP封裝,用戶I/O管腳數(shù)為168個,提供8320個邏輯單元,芯片面積卻僅為34.5mm×34.5mm?本設計中每路跟蹤器占用的邏輯單元為7%,8路跟蹤器外加一些輔助電路總共占用的邏輯單元為60%,芯片資源尚有剩余,為將來系統(tǒng)功能改進留了余地?

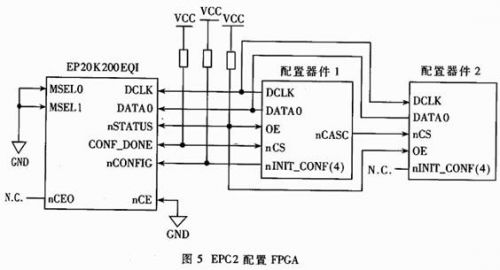

2.2 FPGA芯片的配置

APEX系列FPGA芯片是基于SRAM技術的器件,由于SRAM的易失性,掉電以后芯片中的配置信息將丟失,所以每次系統(tǒng)上電時都要重新加載配置數(shù)據(jù)?Altera公司提供了一系列的配置器件用于儲存配置數(shù)據(jù)并且在上電時加載FPGA?本設計選用Altera公司的EPC2,最大的優(yōu)勢在于EPC2是FLASH器件,可以多次重復編程,改掉了以前的PROM配置器件只能寫入一次的缺點,極大地方便了系統(tǒng)調(diào)試和產(chǎn)品升級?當設計完成的產(chǎn)品需要改進時,只需將EPC2中的內(nèi)容重寫一遍即可,縮短了產(chǎn)品的研發(fā)周期?

在設計中需要注意的是EPC2的容量是1.6Mb,根據(jù)FPGA芯片的容量大小需要的配置芯片的數(shù)目是不等的?本設計中采用的EP20K200EQI芯片的容量是1.9Mb,所以需要兩片EPC2?圖5是用兩片EPC2配置EP20K200EQI芯片的連線圖,通過EPC2芯片的nCASC管腳,可以方便地實現(xiàn)多片級聯(lián)?系統(tǒng)上電后, EP20K200EQI芯片檢測到nCONFIG管腳電平由低到高的跳變時,啟動配置流程?首先EP20K200EQI芯片驅(qū)動CONF_DONE管腳為低,將第一片EPC2的nCS管腳拉低,選通該芯片?經(jīng)過一段延時以后EP20K200EQI芯片釋放nSTATUS管腳,上拉電阻將EPC2的OE管腳拉成高電平將其使能?EPC2用其內(nèi)部振蕩器將配置數(shù)據(jù)串行輸出到FPGA芯片中?當?shù)谝黄珽PC2的全部數(shù)據(jù)輸出完后,它驅(qū)動nCASC管腳為低,按順序驅(qū)動第二個EPC2的nCS為低,啟動第二個EPC2輸出數(shù)據(jù)?前一個EPC2啟動下一個EPC2的過程在一個時鐘周期內(nèi)就可以完成,所以輸送給FPGA芯片的數(shù)據(jù)流是連續(xù)的?

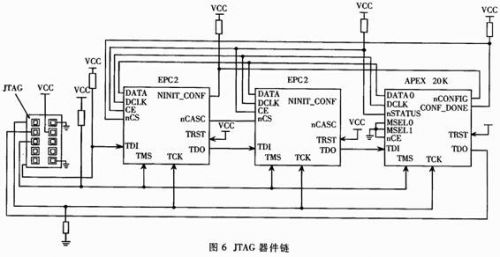

2.3 FPGA芯片的在線編程

APEX系列FPGA芯片在邊界掃描模式(JTAG模式)下可以對其進行在線的配置重構(gòu),系統(tǒng)無需重新上電就可以修改FPGA芯片的配置,極大地方便了調(diào)試?JTAG模式也可以對EPC2進行在線編程?在系統(tǒng)設計時,可以把多個器件組成一個JTAG器件鏈,用一個JTAG兼容頭(例如Altera的ByteBlasterMV并口下載電纜)把所有的器件連接起來?JTAG器件鏈方式特別適合電路板上有多個器件的情況,用一個JTAG頭就可以對多個器件進行在線編程?本設計中電路板上有三個JTAG器件,包括兩片EPC2和一片F(xiàn)PGA,設計的JTAG器件鏈如圖6所示?

在JTAG器件鏈中,兩個EPC2是第一和第二個器件,FPGA是第三個器件,JTAG按順序?qū)ζ骷幊?當對FPGA編程時,通過軟件將兩個EPC2設置成BYPASS模式,編程數(shù)據(jù)從EPC2的TDI管腳直接輸出到TDO管腳直達FPGA芯片,實現(xiàn)了對FPGA芯片的在線編程?采用這種JTAG器件鏈方式,方便了系統(tǒng)調(diào)試,縮短了產(chǎn)品的開發(fā)周期?

3 FPGA應用系統(tǒng)設計中應注意的問題

為了提高FPGA應用系統(tǒng)的抗干擾性能,應盡量采用多層印刷電路板,并有完整的GND層和電源層,從而提供幾乎無限的電流吸收能力,起到防止噪聲和為邏輯信號提供屏蔽的作用?由于APEX EP20KE系列FPGA采用雙電壓體系,最好采用兩個電源層,一個作為核心電源層,一個作為I/O電源層?本設計采用了八層電路板工藝,其中有兩個GND層?一個核心電壓層?一個I/O電壓層以及四個信號層,在實際調(diào)試中抗干擾性能明顯強于以前的雙面板系統(tǒng)?如果在實際應用中對價格敏感,也可采用四層板工藝,其中應有一個完整的GND層,一個分割的電源層?

FPGA器件的每一個電源和GND引腳都應當直接連接到電源和GND平面上,每一對電源和GND引腳都應當接上一個電源去耦電容器,而且盡可能靠近FPGA器件?對于PQFP封裝的器件,應當把去耦電容器集中在器件正下方電路板焊接面上,這樣既達到了靠近器件的目的,又可以減少電路板的面積?

在電源線進入電路板的地方一般都放置一個100μF的大容量電容器,以穩(wěn)定電源電壓,但是這個電容器有時也會成為導致FPGA器件配置失敗的隱患?Altera器件在上電初始化時,首先實行一個POR(上電復位)延遲以等待電源穩(wěn)定?如果電源電壓上升時間較長,超過了POR延遲時間,可能造成器件初始化不正確,導致功能失效?當用EPC2配置APEX EP20KE系列FPGA時,POR延遲最大為200ms,所以電源電壓上升時間不能超過這個時間?如果出現(xiàn)系統(tǒng)上電時FPGA器件配置失敗的情況,應當考慮是否由于大容量電容器致使電源電壓上升太慢,這時可以更換一個小容量的電容器?尤其是在單塊電路板上調(diào)試成功,而多塊電路板連在一起調(diào)試時出現(xiàn)這種情況更應考慮這個原因?因為多塊電路板連在一起時電源濾波電容是并聯(lián)的,此時容量相加導致更大容量的電容出現(xiàn)在電源入口處,致使電壓上升過慢?本系統(tǒng)在調(diào)試時就曾遇見這種情況,將電源濾波電容從100μF調(diào)整為22μF便解決了問題?

為了提高電路設計效率,應盡量多采用LPM宏單元庫?LPM是參數(shù)化的模塊庫,是優(yōu)秀的版圖設計人員和軟件人員智慧的結(jié)晶?LPM包括了常用的邏輯單元,通過修改LPM的某些參數(shù),就能迅速設計出自己的電路?Altera公司提供的LPM宏單元庫是Altera系列FPGA器件的絕佳組合,可以實現(xiàn)絕大部分的設計功能,并能提供較高的運行速度和較低的資源占用率?在設計中發(fā)現(xiàn),多采用LPM宏單元庫的電路與不采用LPM宏單元庫的電路相比,資源占用率可減少10%~30%,可見節(jié)省的芯片資源是很可觀的?

本設計利用FPGA設計靈活?易于編程和容量大的特點實現(xiàn)了多路脈沖重復頻率跟蹤器,解決了在密集信號環(huán)境下跟蹤系統(tǒng)的實時性問題,將八路跟蹤器設計在一片Altera公司的APEX EP20K200EQI FPGA芯片中,縮小了電路體積,滿足了系統(tǒng)小型化的要求?實驗證明用高性能FPGA實現(xiàn)多路脈沖跟蹤系統(tǒng)是完全可行的?

評論